FPGA vivado IP核学习笔记——单端口RAM

1.新建IP

在IP Catalog中找到Block Memory Generator

2.基本配置

①在Component Name位置可以修改IP名字

②Interface Type选择接口类型,有Native(常规)和AXI4两种,AXI4常用于软核控制FPGA或ZYNQ中PS端控制FPGA时使用

③Generate address interface with 31 bits,将地址深度固定在32bit

④Memory Type: 有一下五个选项,本实验选择Single Port RAM

单端口RAM不存在几个端口公用一个时钟的问题,忽略Common Clock

⑤ECC option

在单端口RAM中ECC配置不可选。

ECC介绍

ECC(Error Correcting Code)是指错误纠正编码技术,它可以作为一种附加功能选项集成到RAM模块中。当启用ECC时,RAM会在每个数据字上附加额外的校验位,这些校验位能够在数据读写过程中实时计算并用于检测潜在的位错误。

⑥写入使能

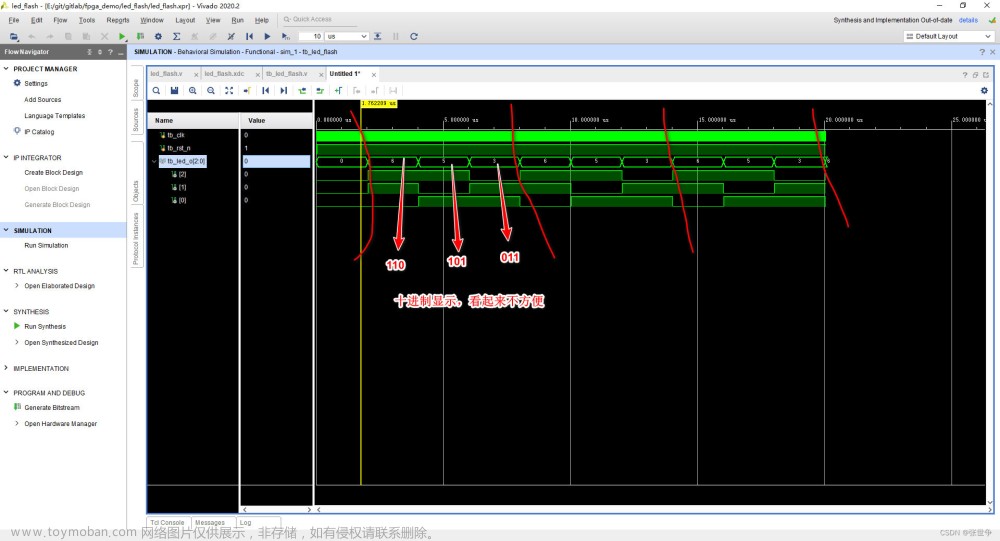

其产品手册有张波形图如上,WEA为写使能端口,高电平有效。以第一个时钟周期为例,b011期间,写入信号DINA为FF EE DD,由于高电平使能写入,故在下一个周期RAM Content存储00 EE DD。

⑦Algorithm Options算法选择

可以选择最小面积、低功耗、固定初始中选择IP生成的优先项,该项保持默认就行。

3.端口A配置

①写入宽度(Write Width): 写入宽度指的是每次向RAM中写入数据的位数,即一次写操作能传输的数据位数。比如,如果写入宽度为32位,那么每进行一次写操作,就可以一次性写入32位的数据。

②读出宽度(Read Width): 读出宽度则是指每次从RAM中读取数据的最大位数。同样以32位为例,如果读出宽度为32位,那么一次读操作就能获取32位的数据。读出宽度通常与写入宽度一致,但在一些高级配置中也可能有所不同。

③写入深度(Write Depth): 写入深度或者说存储深度,指的是RAM可以独立寻址的空间大小,即RAM中可以存储的不同数据单元的数量。例如,一个写入深度为1024的RAM,意味着它有1024个地址,可以存储1024个单位的数据(每个单位的数据宽度由写入宽度确定)。

④读出深度(Read Depth): 在多数RAM IP核中,读出深度与写入深度是一致的,表示RAM可以读取的不同地址的数量。在单端口或多端口RAM中,只要不涉及特殊读写策略,一般无需区分读出深度和写入深度,二者都是指RAM的总存储单元数量。

⑤操作模式

以下是手册上对于三种模式的介绍,可自行查看

⑥Enable Port Type

增加一个输入使能引脚(Use ENA Port),或者一直使能(Always Enable)

⑦Port A Optional Output Registers

询问是否在输出端口A上添加一级寄存器,作为寄存器缓冲层。导致Dout输出信号向后推迟一个时钟周期。这样设计的优点有:

时序优化:通过增加寄存器,可以提供额外的时钟周期延迟,以适应系统设计中的特定时序要求,例如满足建立时间和保持时间约束,或者为接收逻辑提供更多的时间窗口来处理读取的数据。

数据稳定:寄存器可以起到稳定输出数据的作用,确保数据在时钟边沿变化之后已经完全稳定,这对于高速系统或需要高精度数据传输的情况尤为重要。

性能提升:在某些情况下,通过寄存器输出可以提高整体系统的吞吐率,因为读取操作可以在不影响输出数据质量的前提下更快地进行。

⑧ Port A Output Reset Options

通过配置Port A Output Reset Options,设计者可以精确控制在复位条件下端口A输出的行为,包括何时复位以及复位后的初始输出状态。

RSTA Pin:(Reset for Port A)引脚是专门针对端口A输出数据的复位信号。当RSTA信号有效时,端口A的输出寄存器(如果存在的话)将会被复位,从而清除输出数据。这意味着即使RAM中有数据,当RSTA信号触发时,端口A也不会输出任何数据,直到下一个有效的读操作。

Output Reset Value: 这个选项允许设计者配置在复位事件发生时,端口A的输出寄存器预先设定的复位值。当RSTA信号导致复位时,输出寄存器将被重置为预设的复位值,而非随机或未知状态。这对于系统初始化和复位恢复时确保输出数据的一致性和安全性至关重要。

4.其他选项

①Load Init File

允许设计者在RAM实例化之初就加载预先设定的初始数据。当FPGA配置完成并开始运行时,该RAM内的数据就已经填充好了特定的值,而不是默认的随机值。

②Fill Remaining Memory Locations

加载了一个初始化文件来初始化RAM的一部分地址空间后,对剩余未初始化的内存位置进行填充的操作。

③Structural/UniSim Simulation Model Options

是一个与模拟模型相关的选择项,常见于Cadence公司的设计工具中,尤其是用于设计验证环节。这类选项允许设计者在功能仿真阶段选择使用何种级别的模拟模型来模拟RAM(以及其他类似组件)的行为。

④Behavioral Simulation Model Options

文章来源:https://www.toymoban.com/news/detail-861586.html

文章来源:https://www.toymoban.com/news/detail-861586.html

行为级仿真模型选项:是指在进行设计验证时,对RAM或其他复杂逻辑单元选择不同抽象程度的仿真模型进行功能仿真的设置选项。文章来源地址https://www.toymoban.com/news/detail-861586.html

到了这里,关于FPGA vivado IP核学习笔记——单端口RAM的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!