介绍

我给大家介绍的是逻辑/算术左移移位寄存器。实现的功能是根据输入信号shift将输入信号进行移位,高位移除,低位补0。我建立的工程是由3个独立的桶形移位寄存器组成的。

设计文件

library ieee;

use ieee.std_logic_1164.all;

entity barrel is

port( inp : in std_logic_vector(7 downto 0);

shift : in std_logic_vector(2 downto 0);

outp : out std_logic_vector(7 downto 0));

end entity;

architecture behavier of barrel is

begin

process(inp,shift)

variable temp1 : std_logic_vector(7 downto 0);

variable temp2 : std_logic_vector(7 downto 0);

begin

if(shift(0) = '0')then

temp1 := inp;

else

temp1(0) := '0';

for i in 1 to inp'high loop

temp1(i) := inp(i-1);

end loop;

end if;

if(shift(1) = '0')then

temp2 := temp1;

else

for i in 0 to 1 loop

temp2(i) := '0';

end loop;

for i in 2 to inp'high loop

temp2(i) := temp1(i-2);

end loop;

end if;

if(shift(2) = '0')then

outp <= temp2;

else

for i in 0 to 3 loop

outp(i) <= '0';

end loop;

for i in 4 to inp'high loop

outp(i) <= temp2(i-4);

end loop;

end if;

end process;

end architecture;

测试文件

library ieee;

use ieee.std_logic_1164.all;

entity tb_barrel is

end entity;

architecture behavier of tb_barrel is

component barrel is

port( inp : in std_logic_vector(7 downto 0);

shift : in std_logic_vector(2 downto 0);

outp : out std_logic_vector(7 downto 0));

end component;

signal inp,outp : std_logic_vector(7 downto 0);

signal shift : std_logic_vector(2 downto 0);

begin

dut : barrel

port map(inp,shift,outp);

process

variable temp1 : std_logic_vector(7 downto 0);

variable temp2 : std_logic_vector(7 downto 0);

begin

inp <= "01101011";

shift <= "000";

wait for 20ns;

shift <= "001";

wait for 20ns;

shift <= "010";

wait for 20ns;

shift <= "011";

wait for 20ns;

shift <= "100";

wait for 20ns;

shift <= "101";

wait for 20ns;

shift <= "110";

wait for 20ns;

shift <= "111";

wait for 20ns;

end process;

end architecture;

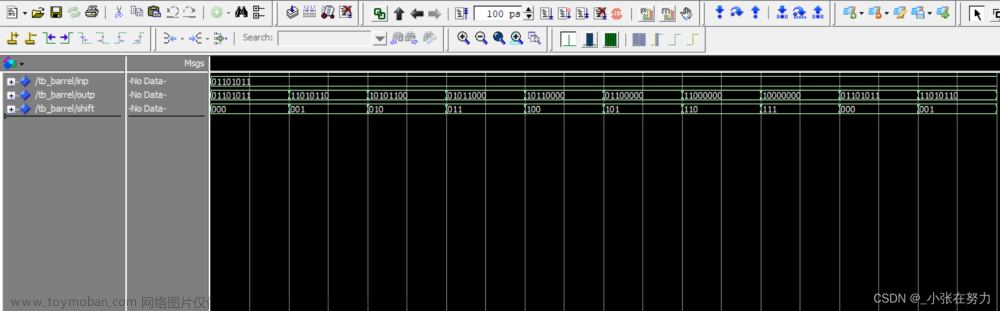

仿真结果

结语

我设计的这个桶形移位寄存器是从shift信号的低位进行判断的,从低位到高位的进位依次是1,2,4。我们可以看到8位数据,通过一个位宽位3的shift信号就可以完成8位移位操作了。

过段时间如果尝试做了循环移位寄存器也会更新的。文章来源:https://www.toymoban.com/news/detail-861797.html

有什么问题大家留言哈。文章来源地址https://www.toymoban.com/news/detail-861797.html

到了这里,关于使用FPGA实现桶形移位寄存器的文章就介绍完了。如果您还想了解更多内容,请在右上角搜索TOY模板网以前的文章或继续浏览下面的相关文章,希望大家以后多多支持TOY模板网!