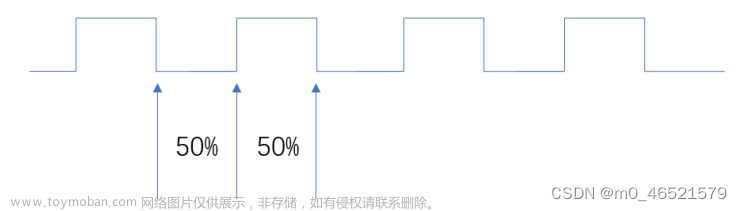

窗口看门狗工作时序

-

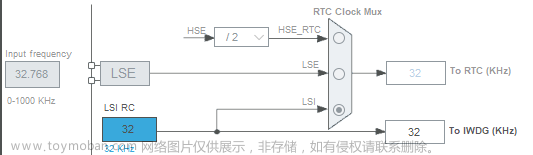

STM32 HAL库 STM32CubeMX -- IWDG(独立看门狗)

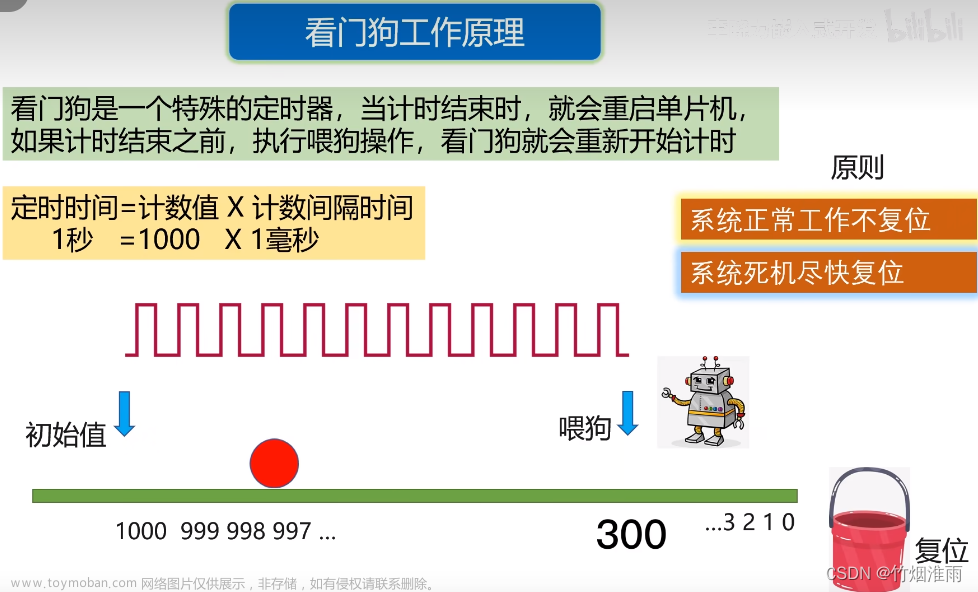

看门狗(Watchdog)就是MCU上的一种特殊的定时器,用于监视系统的运行,在发生错误(例如程序出现死循环)时,能触发一个中断或产生系统复位,防止程序跑飞。STM32 有两个看门狗,一个是独立看门狗另外一个是窗口看门狗,独立看门狗号称宠物狗,窗口看门狗号称警犬。 独立看

-

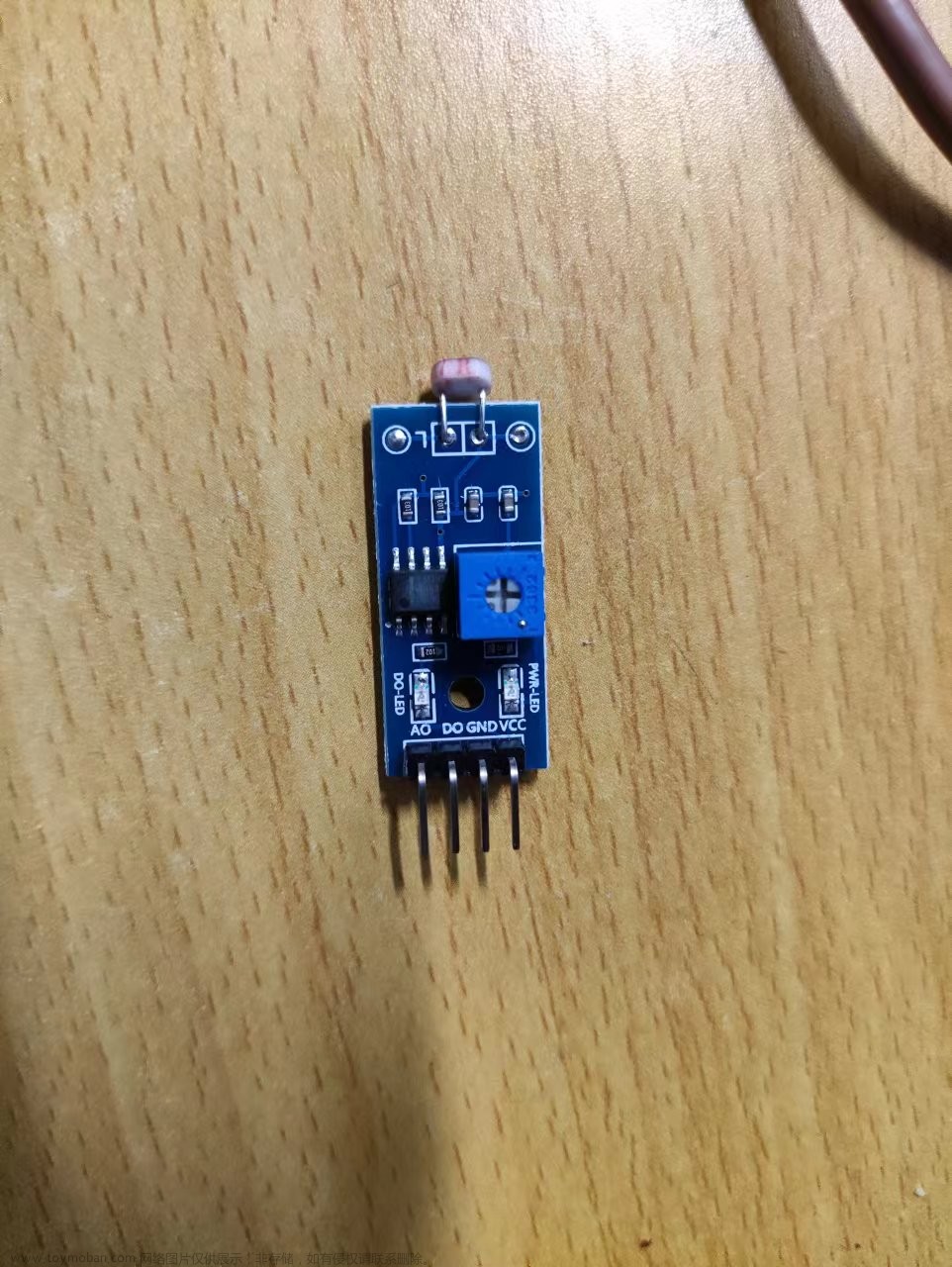

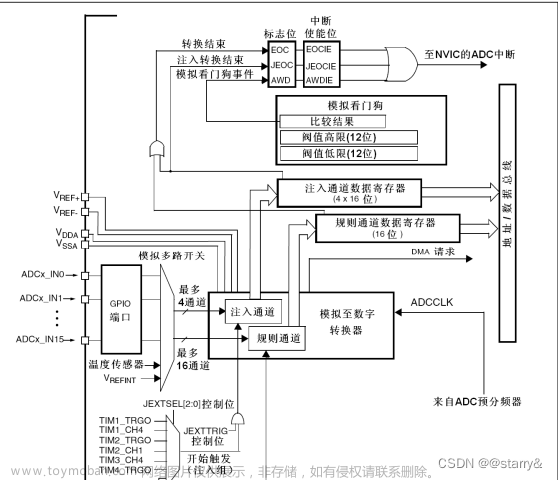

STM32——ADC读取光敏传感器控制LED灯,看门狗中断

一、编写读取AD值的函数,之后判断AD值,进行相应操作,比如点灯。 二、用ADC读取光敏传感器AO口输出,并配置ADC通道看门狗监控这条通道,当光线太暗时打开LED灯。 之后会再介绍可编程RGB灯带WS2812B。 光敏传感器有两个输出口,一个是DO(Digital Output),一个是AO(Analog O

-

【STM32】基础知识 第十五课 看门狗 IWDG 深入理解与应用

STM32 系列单片机具有强大的内置功能, 其中之一就是独立看门口 (IWDG). 看门狗定时器是一种重要的硬件设备, 用于防止系统软件故障. 在许多应用中, 看门狗定时器的使用是至关重要的, 它可以检测和解决软件错误, 提高系统的可靠性. 今天小白将带领大家深入探讨 STM32 独立看门

-

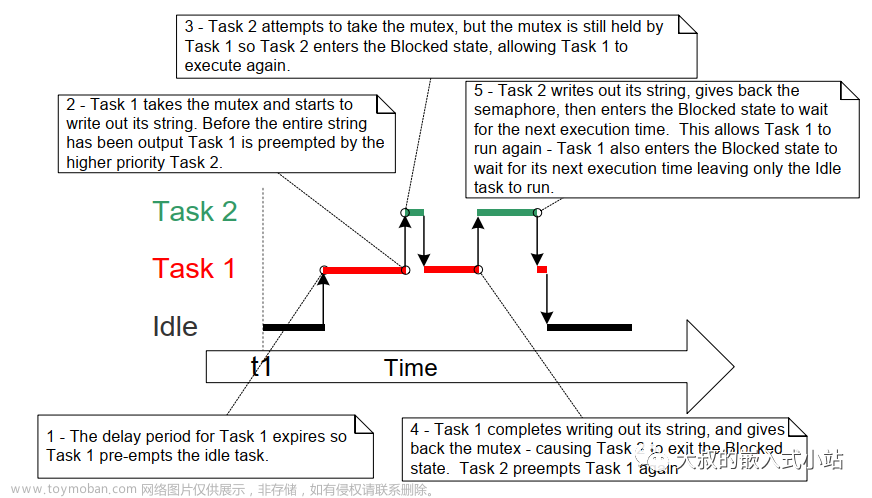

FreeRTOS如何解决访问冲突/线程不安全(临界段、互斥锁、挂起调度、看门人任务)

在多任务(多线程)系统中,存在一个隐患,那就是多线程的访问(在FreeRTOS中就是任务)。当一个任务A开始访问一个资源(外设、一块内存等),但是A还没有完成访问,B任务运行了,也开始访问,这就会造成数据破坏、错误等问题。 例如: 两个任务试图写入一个液晶显示

-

【干货】Android系统定制基础篇:第十六部分(双屏异触、定时开关机与看门狗)

在双屏异显产品中,有时候主副屏都带有触摸屏,并且要求主副屏触摸各自操作互不干扰。 Android 现有框架中已经支持副输入设备的逻辑,只是默认将所有的外部热插拔设备统一指定为副输入设备,这种逻辑我们如果是一个 I2C 加上一个 USB 触摸那么默认就可以支持,USB 触摸

-

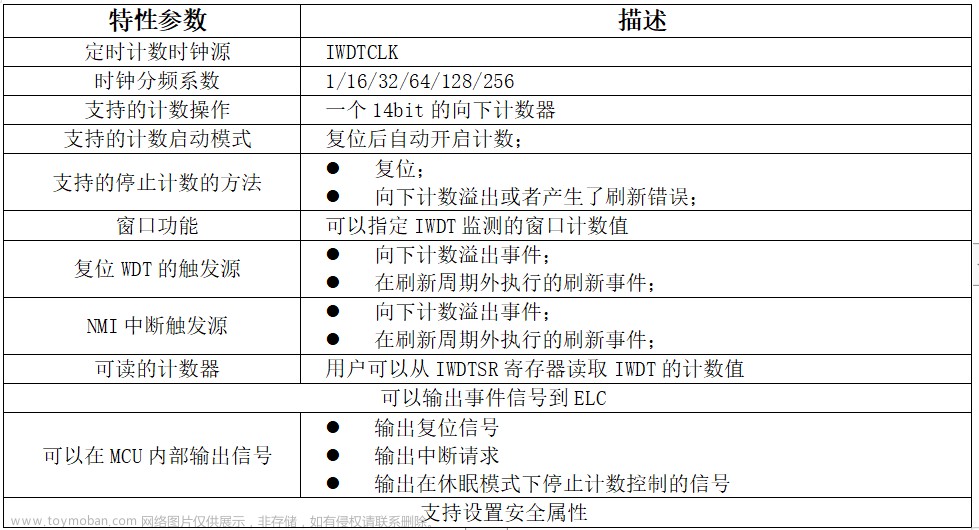

第26章_瑞萨MCU零基础入门系列教程之独立看门狗定时器-IWDT

本教程基于韦东山百问网出的 DShanMCU-RA6M5开发板 进行编写,需要的同学可以在这里获取: https://item.taobao.com/item.htm?id=728461040949 配套资料获取:https://renesas-docs.100ask.net 瑞萨MCU零基础入门系列教程汇总 : https://blog.csdn.net/qq_35181236/article/details/132779862 本章目标 了解A6M5处理器的

-

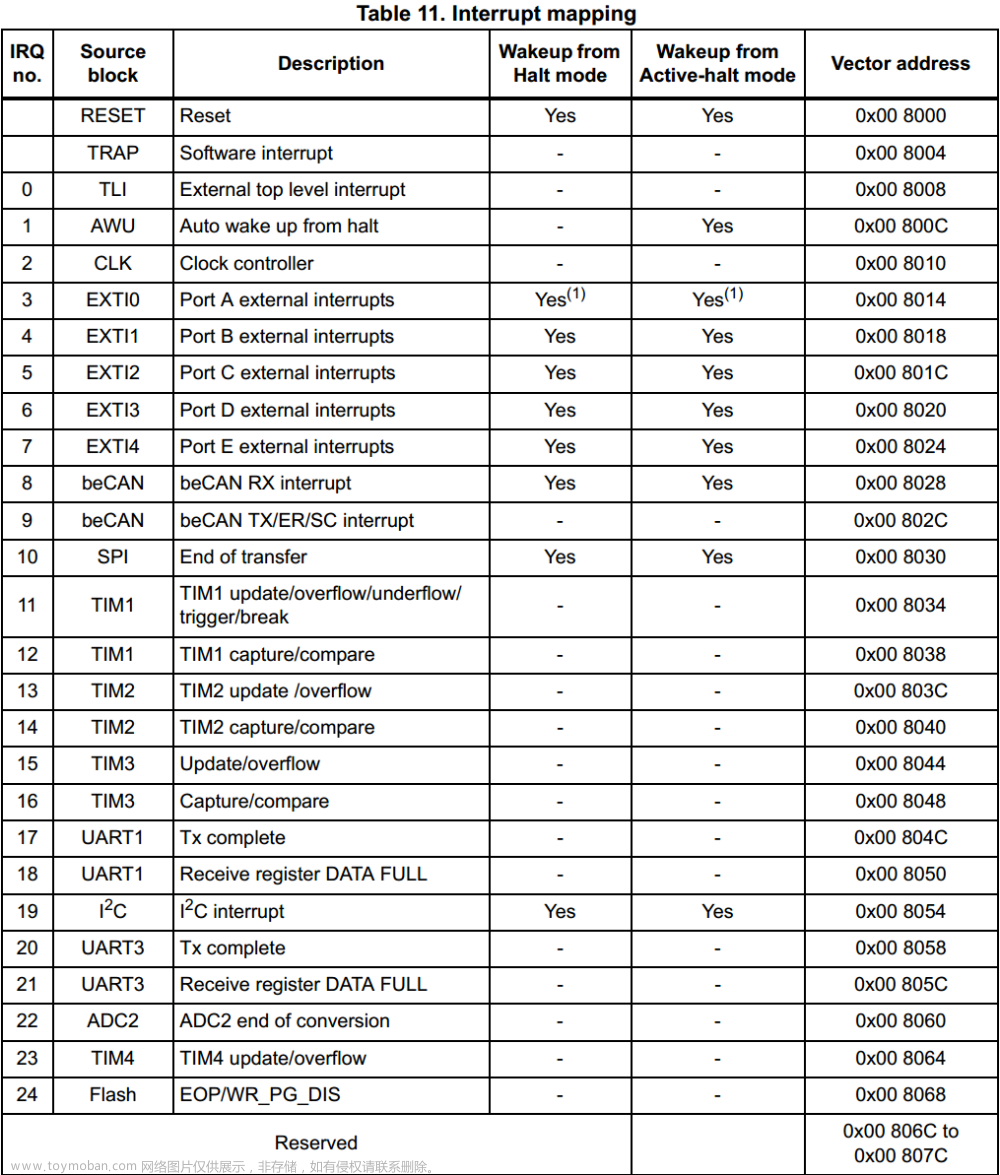

【IAR工程】STM8S208RB基于ST标准库独立看门狗(IWDG)

📍相关篇《【IAR工程】STM8S208RB基于ST标准库下GPIO点灯示例》 🌿《【IAR工程】STM8S208RB基于ST标准库下EXTI外部中断》 🌿《【IAR工程】STM8S208RB基于ST标准库蜂鸣器(BEEP)驱动》 🌿《【IAR工程】STM8S208RB基于ST标准库下自动唤醒(AWU)》 🔖基于ST STM8S/A标准外设库:STSW-STM8069,版本号:

-

STM32_ADC————ADC+DMA多路数据传输,看门狗中断,传感器控制LED

一:介绍ADC与DMA的基本情况与初始化 二:利用ADC+DMA+看门狗中断+传感器控制LED灯代码 三:总结实验过程中碰到的错误与问题 通过DMA转运ADC的数据,设置ADC的中断看门狗阈值,当光敏传感器的ADC采样值在看门狗高低阈值中间,不触发中断,如果超过看门狗的高低阈值就会触发

-

ARM day7 day8 UART串口、PWM蜂鸣器、WDT看门狗、ADC数模转换

GPA1_0: RXD2 GPA1_1: TXD2 1)对外设置 (GPIO) GPA1CON: 0x11400020 3:0-0x2(RXD2) 7:4-0x2(TXD2) 2)对内设置(uart) ULCON2: 0x13820000 0x3 UCON2: 0x13820004 1:0-01(polling) 3:2-01(polling) UTRSTAT2: 0-1(r

-

【面试 分布式锁详细解析】续命 自旋锁 看门狗 重入锁,加锁 续命 解锁 核心源码,lua脚本解析,具体代码和lua脚本如何实现

自己实现锁续命 在 controller 里开一个 线程 (可以为 守护线程) 每10秒,判断一个 这个 UUID是否存在,如果 存在,重置为 30秒。 如果不存在,守护线程 也结束。 基本的key value 基本的使用 setIfAbsent存在不设置 16384 Redis 集群没有使用一致性hash, 而是引入了哈希槽的概念。 R

-

看门狗的详细介绍(重点:喂狗操作应该在主循环或其他正常运行的代码段中执行,而不是在中断服务函数中进行)

1. 看门狗的作用是:当单片机因为软硬件问题或者外界干扰导致死机时,可以自动复位单片机,使系统重新正常工作。 当电脑的系统死机了,我们可以人为手动的进行重启,使电脑重新正常工作。但当火星的单片机系统死机了,我们没办法人为的去重启,只能靠这只看门狗来

-

时序分析、时序约束和时序收敛(1)--时序分析、时序约束和时序收敛分别都是什么?

文章目录 写在前面 磨刀不误砍柴工 什么是时序分析? 什么是时序约束? 什么是时序收敛? 时序约束与分析是FGPA开发过程中一项必备的技能,同时也是设计开发中相对较难的部分。很多人一谈起FPGA开

-

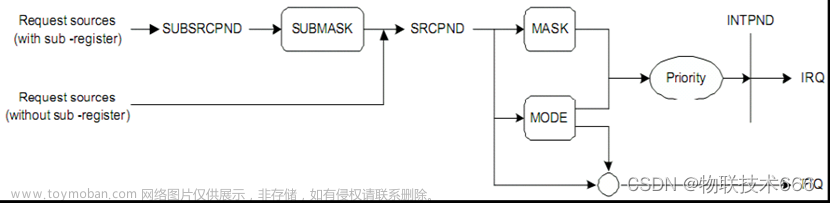

嵌入式培训机构四个月实训课程笔记(完整版)-Linux ARM驱动编程第二天-ARM中断、定时器、看门狗(物联技术666)

链接:https://pan.baidu.com/s/1E4x2TX_9SYhxM9sWfnehMg?pwd=1688 提取码:1688 上午:中断 吕峰老师 下午:定时器 教学内容: 一、中断 ARM 中断分为二级,分为一级中断和二级中断,二级中断为子中断,对于 ARM 来说有 50 个中断源, 其中有 32+ ( EINT23-4 ) 23-4+1-2=50 子中断源

-

时序分析、时序约束和时序收敛(6)--如何读懂一个时序报告?

目录 写在前面 1、建立工程与添加时序约束 2、时序报表 在之前的文章中写了一些时序分析的基础概念,同时还说了文章中提到的公式根本就不需要记忆,因为综合工具vivado会帮你把所有时序路径都做详尽的分析,你所需要做的就是理解概念。 光说不

-

FPGA时序分析与约束(2)——时序电路时序

在之前的内容中,我们介绍了组合电路的时序问题和可能导致的毛刺,强烈推荐在阅读前文的基础上再继续阅读本文, 前文链接:FPGA时序分析与约束(1)——组合电路时序 这篇文章中,我们将继续介绍FPGA时序分析相关内容,本文介绍的是时序电路的时序

-

FPGA时序分析与时序约束(四)——时序例外约束

目录 一、时序例外约束 1.1 为什么需要时序例外约束 1.2 时序例外约束分类 二、多周期约束 2.1 多周期约束语法 2.2 同频同相时钟的多周期约束 2.3 同频异相时钟的多周期约束 2.4 慢时钟域到快时钟域的多周期约束 2.5 快时钟域到慢时钟域的多周期约束 三、虚假路径约束 四、最

-

《时序分析、时序约束和时序收敛》专栏的说明与导航

知识付费时代,多做一些尝试 免费内容非常容易被其他网站爬虫获取,付费是某种意义上的版权保护 付费即意味着责任,有利于提高专栏质量,驱使作者对读者、对内容更负责 本专栏内容均与FPGA的时序分析、约束、优化和收敛相关,是真真正正能用起来的 实战

-

FPGA的时序分析、约束和收敛(1)----什么是时序分析?什么是时序约束?什么又是时序收敛?

文章目录 写在前面 磨刀不误砍柴工 什么是时序分析? 什么是时序约束? 什么是时序收敛? 时序约束与分析是FGPA开发过程中一项必备的技能,同时也是设计开发中相对较难的部分。很多人一谈起FPGA开

-

时序分析、时序约束和时序收敛(8)--关于时序路径、时钟悲观度和建立时间/保持时间的一些问题

目录 写在前面 1、为什么同一条时序路径在报表里的值不一样?

-

静态时序分析与时序约束

理性的时钟模型是一个占空比为50%且周期固定的方波: 实际电路中输入给FPGA的晶振时钟信号是正弦波: Clock Jitter,时钟抖动,相对于理想时钟沿,实际时钟存在不随时钟存在积累的、时而超前、时而滞后的偏移。 Clock Skew:时钟偏差,同一个时钟域内的时钟信号到达数字电