窗口看门狗verilog代码是多少

-

【FPGA实现三态门(inout)Verilog代码详解】

【FPGA实现三态门(inout)Verilog代码详解】 三态门(tristate gate)是在数字电路中使用频率较高的一种逻辑门,其特点是输出端具有三种可能的状态:高电平、低电平和高阻态。在实际应用中常常用于多个设备共享同一个总线的情况下,有效地防止输出口相互影响、产生干扰等

-

FPGA实现Verilog 2分频:从原理到代码实现

FPGA实现Verilog 2分频:从原理到代码实现 在数字电路设计中,2分频是一种常见的电路实现方式,可以将输入信号的频率减半。在FPGA设计中,我们可以利用Verilog语言快速实现2分频电路。本文将从原理出发,结合代码介绍FPGA实现2分频电路的方法。 原理及实现 2分频电路通常采

-

微波炉控制器Verilog代码Quartus仿真

名称:微波炉控制器Verilog代码Quartus仿真(文末获取) 软件:Quartus 语言:Verilog 代码功能: 微波炉控制器 用芯片Altera Cyclone IV FPGA作为控制芯片,实现时间设置、温度设定、火力选择、声音提示,在硬件组成上,涉及到电源供电、按键输入、数码管显示、指示灯提示等。 由按

-

Quartus波形发生器频率可调verilog代码仿真

名称:Quartus波形发生器频率可调verilog代码仿真(文末下载) 软件:Quartus 语言:Verilog 代码功能: 波形发生器频率可调 可产生正弦波,锯齿波,三角波,方波4种波形(频率可调), 2.具有波形选择、起动、停止功能。 设计文档.doc 1. 工程文件 2. 程序文件 3. 程序编译 4. RTL图

-

Vivado:ROM和RAM的verilog代码实现

本文主要介绍ROM和RAM实现的verilog代码版本,可以借鉴参考下。 Read-only memory(ROM)使用ROM_STYLE属性选择使用寄存器或块RAM资源来实现ROM,示例代码如下: RAM设计方式有很多,可以用BRAM、LUT、分布式RAM、URAM实现,可以使用RAM_STYLE属性强制规定使用的资料类型。 (*rom_style = \\\"bl

-

自助点餐机Verilog代码远程云端平台Quartus

名称:自助点餐机Verilog代码远程云端平台Quartus 软件:Quartus 语言:Verilog 代码功能: 自助点餐机设计, 商品分为7、9、14元三种套餐, 并且只接受5、10元两种面值的纸币: 可以一次点多份: 用数码管显示购买数量、所需金额、找零金额,当金额不足时通过蜂鸣器提示 本代码已

-

VScode配置verilog环境(代码补全,报错,波形仿真)

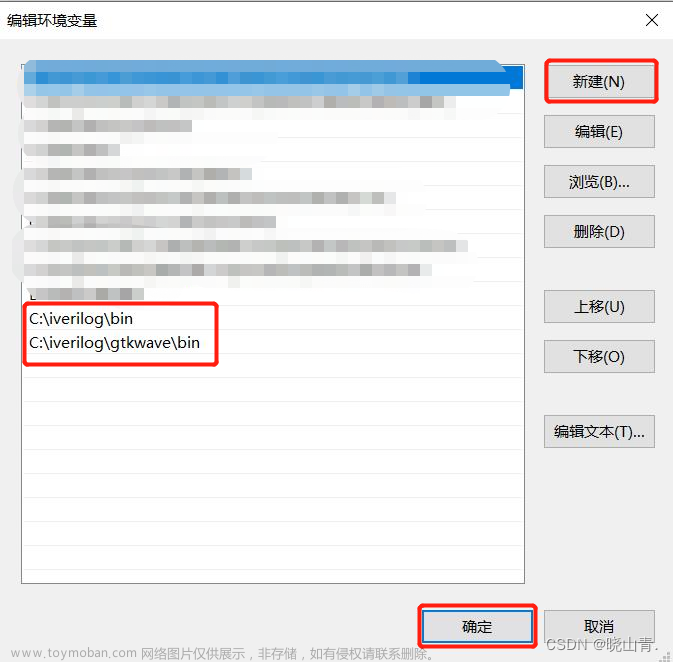

在win11的系统里,ise软件不能运行,而在虚拟机中ise的配置也很费劲,今天在这里教大家在VScode中玩转Verilog。 实现代码补全、代码高亮、错误检查 实现生成Testbench 实现波形仿真 iverilog(自带gtkwave)、ctags.exe 所需配置文件 官方下载网址 (速度较慢) iverilog:Icarus Verilog for Windows

-

基2-booth乘法器原理及verilog代码

对于一个n位的有符号二进制数B,首位是0则B可以表示为: 首位是1,B[n-2:0]是实际数字的补码,所以可以得到 。 可以得到合并的公式如下所示: 将公式展开: 除了n-1项外的每一项乘2之后再减去本身: 根据2^i重构公式: 为了统一形式,添加一项B[-1],初始值为0.注意这里的B

-

流水线乘法器的原理及verilog代码

二进制数乘法的显著特点就是可以将乘法转换为移位,乘2就是左移一位,乘2^n就是左移n位。而一个二进制数又可以看成是由若干个2的i次方的和。 设被乘数和乘数分别为M、N,且都是32位的二进制数,乘积结果为64位 的向量CO则 。 所以乘法可以由移位电路和加法器完成。计算

-

MATLAB生成Verilog代码——HDL Coder使用初探

有关用HDL Coder生成Verilog的资料实在太少,且大多是由Simulink搭建模块生成。笔者经过初步探索,将MATLAB代码直接通过HDL Coder生成Verilog代码的过程总结于此。 以一个最大值为15可加减计数器为例 在MATLAB上方的APP里找到HDL Coder,HDL Coder需要MATLAB Function和MATLAB Testbench两个文件,第

-

智能抢答器Verilog代码Quartus远程云端平台

名称:Quartus智能抢答器Verilog代码远程云端平台 软件:Quartus 语言:Verilog 代码功能: 设计要求 (1)设计语言为Veri1og,硬件开发平台为 Spartan-3E开发板。数码管显示倒计时5秒;每名选手抢到后由数码管显示其得分增加1,一共进行 (2)设计基于FPGA的智能抢答器的设计,要求有四

-

FPGA学习笔记:verilog基础代码与modelsim仿真(三)

1. 分频器——偶分频 方法1: verilog代码实现: modelsim仿真波形图: 方法2(推荐): 比起方法一直接使用计数器定义一个新的时钟波形,方法二使用flag_out作为分频变量从而实现分频器的功能。虽然二者都使用了计数器,但方法二显然更符合“分频”的定义,且此方法在告诉

-

地铁售票设计Verilog代码AX301开发板Quartus

名称:Quartus地铁售票设计Verilog代码AX301开发板 软件:Quartus 语言:Verilog 代码功能: 主要内容: 1选择1号或者2号地铁线,每条线都有3元,4元,5元二种票价 2选择买张或者两张。乘客在操作失误时,可以进行清零然后重新购买。 3投钱可以选择1元,5元,10元, 4比较投钱和票价。投钱和

-

verilog键盘输入示例代码及分析(摩尔型有限状态机)

往昔鸳鸯戏水,而今不相依偎,美景良辰纵然抚媚亦徒留伤悲。----《美人画卷》 本代码是一生一芯项目中,南京大学nvboard开源项目键盘扫描示例代码。我们抛开上层连接不谈,分析一下这个代码。同时我自己也理清一下思路,不然总是感觉些许混乱,或者说,明明用51单片

-

Verilog代码生成FPGA仿真波形文件(VCD)介绍

Verilog代码生成FPGA仿真波形文件(VCD)介绍 在FPGA设计中,我们需要对设计的电路进行仿真以检查其正确性。VCD(Value Change Dump)文件是一种常用的仿真波形文件格式,可以记录电路仿真过程中各个信号的变化情况。本文将介绍如何使用Verilog代码来生成VCD文件。 首先,我们需

-

verilog手撕代码3——序列检测和序列发生器

2023.4.25 2023.4.26 学习打卡,天气转晴 1.1.1 序列缓存对比/移位寄存器法 把输入的数据缓存到数组,然后与目标进行对比 例1 :检测序列 0111_0001 ,满足序列输出为1 例2 :检测序列 1101 ,用移位寄存器实现 例3 : 含有无关项的序列检测 检测序列 001_xxx_110 ,中间三位不关心,这

-

等精度频率计verilog,quartus仿真视频,原理图,代码

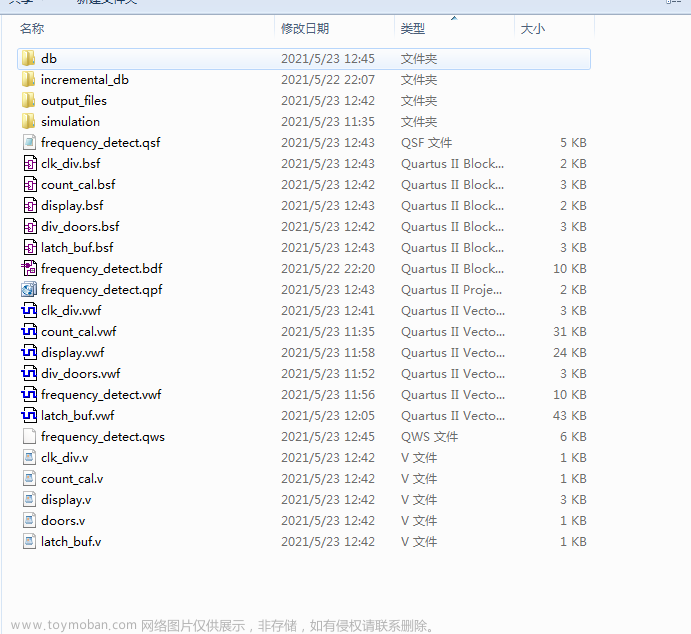

名称:等精度频率计设计verilog quartus仿真 软件:Quartus 语言:Verilog 要求: A:测量范围信号:方波 频率:100Hz~1MHz; B:测试误差:0.1%(全量程) C:时钟频率:50kHz D:预闸门时间:01s E:系统时钟频率:50MHz F:频率计算:保留1位小数 本代码下载:等精度频率计设计verilog,quartus仿真

-

基于FPGA的MSK调制波形Verilog代码Quartus仿真

名称:基于FPGA的MSK调制波形Verilog代码Quartus仿真(文末获取) 软件:Quartus 语言:Verilog 代码功能: 基于FPGA的MSK调制波形 1、输入调制原始数据,输出MSK调制波形 2、包括差分编码模块,MSK调制模块,DDS模块,有符号乘法器模块等 1. 工程文件 2. 程序文件 3. 程序编译 4. RTL图

-

初学Verilog语言基础笔记整理(实例点灯代码分析)持续更新~

实例:点灯学习 刚接触 Verilog ,作为一个硬件小白,只能尝试着去理解,文章未完…持续更新。 参考博客文章: Verilog语言入门学习(1) Verilog语法 【 Verilog 】一文带你了解 Verilog 基础语法 - 子墨祭的文章 - 知乎 关于Verilog中的几种赋值语句 这里抄点,那里扣点,整理了一

-

基于FPGA的音乐喷泉控制Verilog代码Quartus仿真

名称:基于FPGA的音乐喷泉控制Verilog代码Quartus仿真(文末获取) 软件:Quartus 语言:Verilog 代码功能: 基于FPGA的音乐喷泉控制 1、具有启动控制按键,按下后开始 2、喷泉具有6个喷嘴,可以手动切换三种工作模式 3、输入的音乐信号分为低音、中音、高音 4、将输入的音转换为